`elsif D01 reg t01;2) `ifdef 宏名 (标识符) 程序段1 `endif 这里的 "宏名" 是一个Verilog HDL的标识符,"程序段"可以是Verilog HDL语句组,也可以是命令行。这些命令可以出现在源程序的任何地方。注意:被忽略掉不进行编译的程序段部分也要符合Verilog HDL程序的语法规则。Verilog `ifdef `elsif Example The following example has two display statements inside separate `ifdef scopes which does not have a default `else part to it So this means that by default nothing will be displayed If the macro either MACRO is defined,

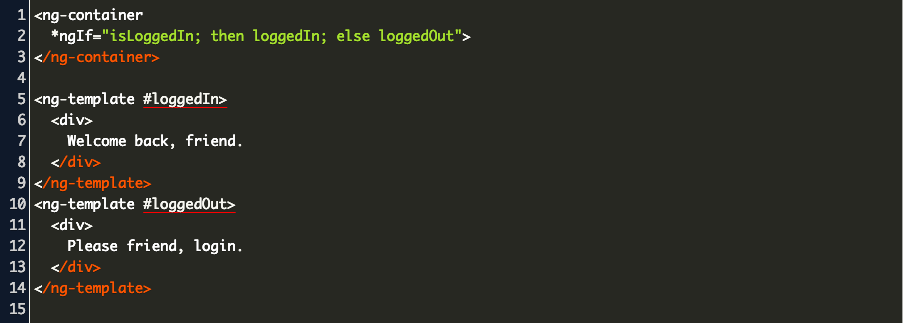

Ngifelse Code Example

Verilog ifdef elif

Verilog ifdef elif-SystemVerilog 05 `` `" `\`" SystemVerilog 09 `define MACRO(arg=default) `undefineall3341 今天在参考大佬的RS232 Receiver的时候,用到了 `ifdef 指令,我虽知道它是 条件编译 指令,但是内容已经忘了差不多了,也不敢胡乱猜测。 今天趁此机会总结一下: 一般情况下, Verilog HDL源程序中所有的行都参加 编译 。 但是有时候希望对其中的一部份内容

The C Preprocessor Gnu Project Ifdef 36 4 2 2 If The C Preprocessor Often Known As Cpp Is A Macro Processor That Is Used Automatically By Pdf Document

The #elseif, #else, and

No comments:

Post a Comment